- 專利名稱(中文) / 針對無線多重輸入輸出系統預編碼技術之高效率幾何平均分解矽智財設計

- 專利名稱(英文) / Efficient Geometric Mean Decomposition Silicon IP design for Digital Precoding in Wireless MIMO communication systems

- 所屬單位(一級單位) / 工學院

- 所屬單位(二級單位) / 電機工程學系

- 發明人(中文) / 黃穎聰

- 發明人(英文) / Yin-Tsung Hwang

- 申請國家 /

- 專利類型 /

- 專利證書號 / 低複雜度的預編碼方法,中華民國專利,發明第I469558號

- 技術成熟度 /

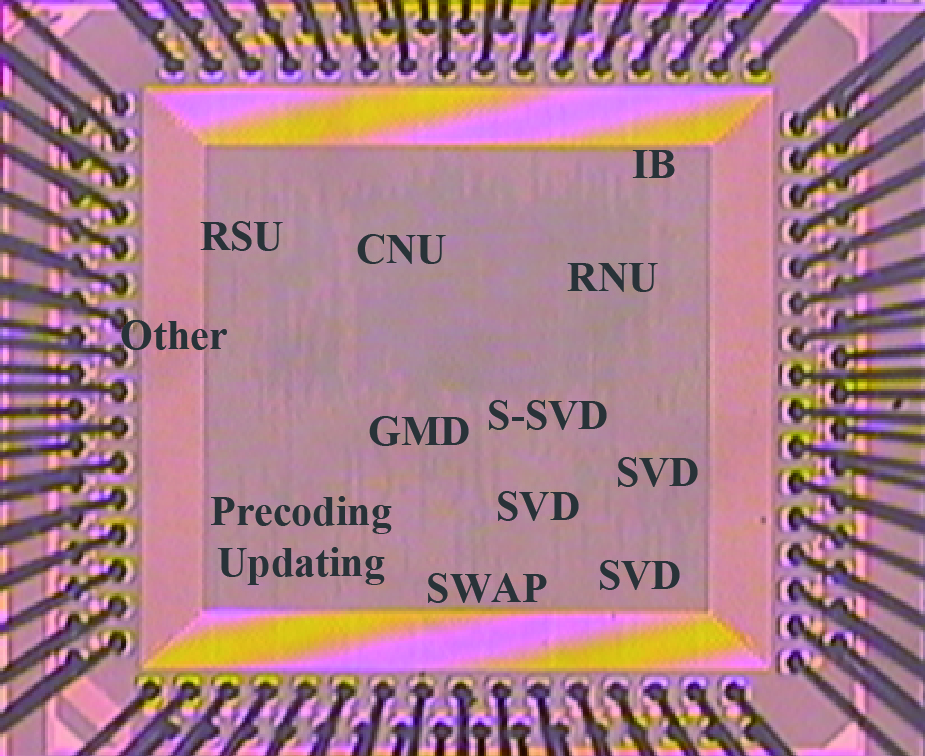

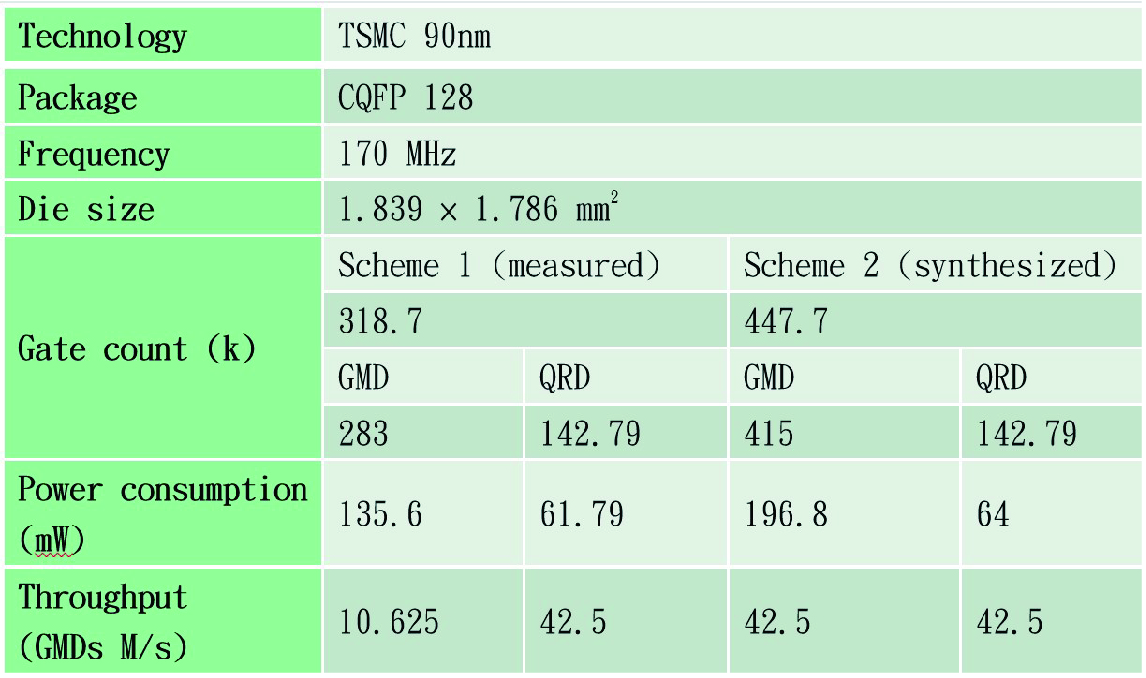

數位預編碼是提昇多重輸入輸出無線通訊系統效能的重要訊號處理技術。然而這個技術需要大量的矩陣運算,對系統即時運算的需求造成很大的負擔。本技術海報要介紹的是一個高運算效率、利用幾何平均分解的數位預編碼矽智財設計,可以顯著提升訊號偵測效能近似於MLD最佳解碼器。本設計的特點是避開了繁複迭代式的奇異值分解的做法,因而不用考慮到演算法收斂的問題。它並採用了問題切割解決的做法,大幅降低了運算複雜度並開發出許多平行運算的契機,改善晶片設計的效能。本設計架構可以輕易的套用到不同的系統組態架構,並且能以矽智財的方式整合到包括4G/5G以及802.11ac WiFi等的通訊系統的基頻處理器設計。本矽智財已經利用台積電90nm製程驗證,最高可工作在170百萬赫茲,每秒可執行42.5百萬次的預編碼,以4X4 系統組態64QAM調變機制,其傳輸資料速率可達1.02Gbps。

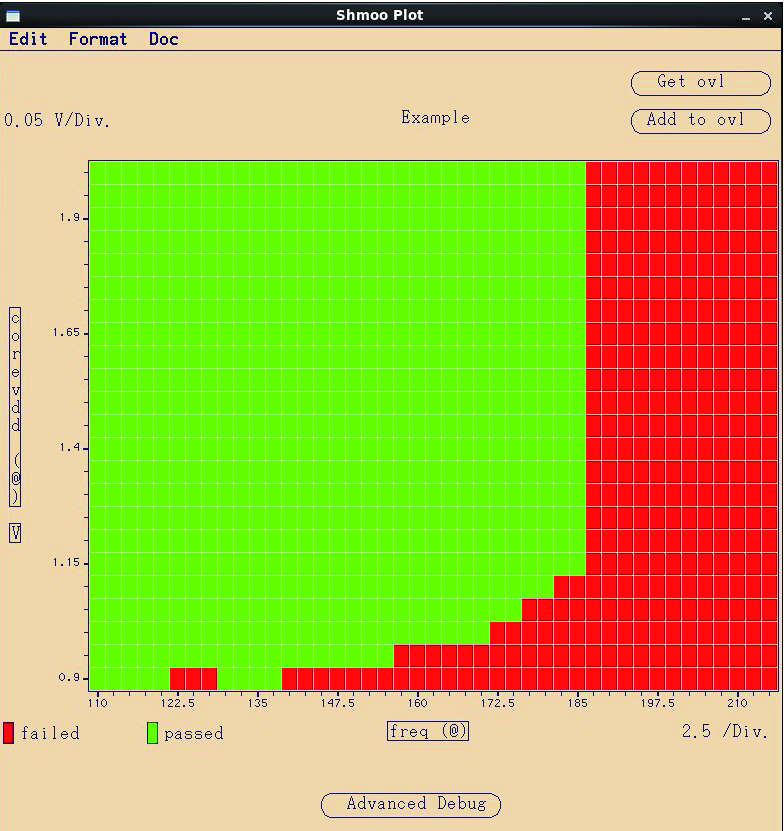

Digital precoding is an essential signal processing technique to enhance the performance of wireless Multiple Input Multiple Output (MIMO) communication systems. The scheme, however, imposes tremendous computing overheads in the form of matrix operations, which becomes a formidable barrier in real time processing. The technique presented in this poster is an efficient geometric mean decomposition (GMD) based precoding design capable of facilitating asymptotically equivalent performance of maximum likelihood detector (MLD). It requires no iterative singular value decomposition (SVD) as pre-processing and is thus exempted from the convergence problem. The divide-and-conquer approach reduces the computing complexity and provides abundant computing parallelism. The design features lower computing complexities, higher throughput rate, and hardware sharing between the pre-coding and the signal detection modules. In addition, the IP design is easily adaptable to different MIMO configurations and can be applied to various wireless communication systems such as 4G/5G and 802.11ac WiFi. A unified GMD/QRD chip using a fully parallel and deeply pipelined architecture is developed to verify the proposed design. One GMD or QRD computation on a 4×4 complex-valued matrix can be accomplished every 4 clock cycles. Chip implementation in TSMC 90nm CMOS technology shows that, with a maximum clock frequency up to 170MHz, the design can perform 42.5M GMD computations per second. The equivalent data rate is 1.02Gbps for a 64QAM modulation scheme.

無線通訊基頻晶片,數位預編碼,幾何平均分解法

Wireless Communication Baseband Chip, Digital Precoding, Geometric Mean Decomposition Scheme